# 1-8 GHz High Efficiency Single Stage Travelling Wave Power Amplifier

Mustafa Sayginer<sup>1</sup>, Metin Yazgi<sup>1</sup>, H. Hakan Kuntman<sup>1</sup>, Bal S. Virdee<sup>2</sup>

<sup>1</sup>Istanbul Technical University, Faculty of Electrical and Electronics Engineering, Department of Electronics and

Communication Eng., 34469, Maslak, İstanbul, TURKEY

sayginer@itu.edu.tr, yazgim@itu.edu.tr, kuntman@itu.edu.tr

<sup>2</sup>London Metropolitan University, Faculty of Computing, Centre for Communications Technology,

166-220 Holloway Road, London N7 8DB, U.K.

b.virdee@londonmet.ac.uk

# Abstract

In this paper a Class-A/AB operated wideband power amplifier is presented that comprises of only a single transistor travelling wave stage where capacitive coupling and frequency dependent lossy artificial transmission-line are employed at the input of the active device. These technique are shown to significantly enhance the amplifier frequency-bandwidth product, input match and gain flatness performance over 1-to-8 GHz operating bandwidth. Furthermore, a non-terminated output artificial transmission line inductance is determined using load-pull data to achieve an optimum power-bandwidth performance. Overall 1.31×2.93mm<sup>2</sup> power amplifier design is fabricated by using 0.25µm GaAs PHEMT MMIC process and the amplifier delivers 1W and 0.5W peak Psat and Pout,1dB levels respectively where the PAE levels are over 50% and 27% for P<sub>sat</sub>, and P<sub>out,1dB</sub> almost the entire 2-to-8 GHz frequency band.

#### 1. Introduction

The basic idea underpinning the travelling wave amplifiers (TWA) is the use of inherent parasitic capacitances at the transistor's input and output terminals together with external inductive elements to form artificial transmission-lines [1-4]. The cut-off frequency of the amplifier circuit is therefore determined by the cut-off frequency of the artificial-lines. The resulting amplifier structure readily provides broadband performance, usually above one decade. There are basically two classes of TWA structures in the literature: Conventional TWA (CTWA) [1, 2] and Cascaded Single-Stage TWA (CSSTWA) [3-5]. In a single transistor case both classes reduce to the same structure and the power amplifier could be denoted as Single-stage travelling wave power amplifier (SSTWPA) [6].

The SSTWPA has some disadvantageous namely poor broadband gain flatness and matching. However, these drawbacks can be eradicated by properly designing the amplifier circuit using techniques such as capacitive coupling [2] and frequency dependent lossy artificial-line [5].

In this paper, the proposed SSTWPA structure employs both technique of capacitive coupling and frequency dependent lossy artificial transmission-line at the FET input terminal. The FET output artificial transmission-line inductive element is determined by using load-pull data of the transistor and the termination impedance is removed to improve output power performance. The design procedure presented here provides wideband operation using a single device with the high efficiency performance. SSTWPA circuit is designed and fabricated by using  $0.25\mu m$  GaAs PHEMT process from United Monolithic Semiconductor.

# 2. Analysis of SSTWPA

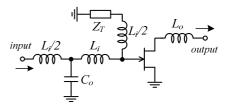

A general and simplified topology of the SSTWPA circuit is depicted in Fig. 1 [6]. The input signal propagates along the input artificial transmission-line and stimulates the active device gate terminal.  $Z_T$  is the termination impedance of the input-line. The amplified signal at the output goes through the output line formed by the output capacitance of the FET device and the series inductance  $L_o$ .

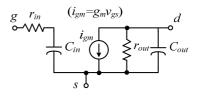

The simplified small-signal equivalent circuit model representing the transistor shown in Fig. 2 is preferred for basic ac-analysis of TWA [7]. This model includes input ( $C_{in}$ ) and output ( $C_{out}$ ) parasitic capacitances, input serial resistance ( $r_{in}$ ) and output parallel resistance ( $r_{out}$ ). The capacitances form artificial transmission-lines with the external inductive components.

The magnitudes of the device resistive elements have the most effect on the performance of the input artificial-line. This simple model however cannot predict the device behavior completely but by investigating variations of the parameters in the model versus frequency, it is possible to predict the gainfrequency performance.

Fig. 1. Simplified schematic of the SSTWPA.

Fig. 2. Simplified active device model.

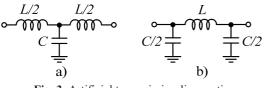

Fig. 3. Artificial transmission-line sections: (a) T- type (b)  $\pi$ -type sections

Two types of artificial transmission-line sections can be defined as T-type and  $\pi$ -type shown in Fig. 3. Typically artificial-lines in a TWA are designed using T-type sections. However, for the circuit analysis purpose, the  $\pi$ -type approach at the input and output of the transistor is necessary due to the capacitive behavior of the input and output ports of the active device.

Artificial transmission-lines in a TWA behave like low-pass filter characteristics which have characteristic impedance and for the lossless case the cut-off frequency given by

$$Z_o = \sqrt{L/C} \tag{1}$$

$$f_C \cong 1/\pi \sqrt{LC} \tag{2}$$

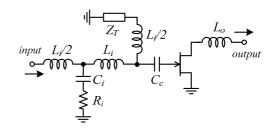

As will be shown later the frequency dependent lossy artificial transmission-line section at the input can improve gain-frequency performance of the SSTWPA. In Fig. 4, an SSTWPA input line is shown to employ one lossy T-section comprising of a resistor ( $R_i$ ). This lossy section has not only an effect of improving the input matching and gain flatness but also it helps to ensure stability of the amplifier. Furthermore, the SSTWPA in Fig. 4 also employs a capacitance ( $C_c$ ) in serial to the transistor input to increase the frequency-bandwidth [2]. This technique of capacitive coupling however reduces the amplifier gain as a drawback.

The other important design step for the SSTWPA is the loadpull characterization in order to determine an appropriate output-line inductance. Limiting the magnitude of the inductance at the output of a SSTWPA is also important since the high frequency loss increases when the inductance value is high and therefore it can affect the amplifier's overall output power performance.

Moreover, a single inductance simplifies the amplifier's construction. As will be shown later this artificial transmissionline technique is advantageous for broadband applications. Hence, it can be deduced that the circuit given in Fig. 4 is a convenient structure for broadband power applications.

In Fig. 4, values of capacitance and resistance of the lossy section simply could be given by

$$C_i \cong \frac{C_{in}C_c}{C_{in} + C_c} \tag{3a}$$

$$R_i \cong r_{in}$$

(3b)

The value of the inductance at the input line is calculated to provide characteristic impedance of  $Z_0$ , equal to

$$L_i = Z_o^2 C_i \tag{4}$$

As mentioned above, the output inductance value is determined by load-pull analysis and the output line characteristic impedance  $(Z_{opl})$  is obtained by using

$$Z_{opt} = \sqrt{L_o/C_{out}} \tag{5}$$

If  $Z_{opt}$  is not equal to 50 $\Omega$  then by using an impedance matching network or a transformer at the output may help to enhance the amplifier power performance. The small-signal gain of the modified SSTWPA could be given by

$$\left|A_{o}\right| \cong \left(\frac{C_{c}}{C_{in} + C_{c}}\right) g_{m} Z_{opt} \tag{6}$$

The expressions given above were used in the first step of designing the SSTWPA. It should be noted that the obtained circuit may not provide the optimum performance because of the unaccounted inherent parasitic effects. In this case it is necessary to instigate optimization steps in order to improve the gain flatness performance of the SSTWPA in the desired frequency band of operation.

# 3. Design of the SSTWPA Circuit

The SSTWPA circuit is designed according to the previous discussion. The design aim is to maximize power performance over the widest possible frequency band of the amplifier.

The first step of the design process involves determining suitable transistor dimensions and choosing the bias point. Thus, a single transistor having maximum channel width of 125 $\mu$ m and 12 fingers geometry is selected. For this device I<sub>D</sub>=140mA and V<sub>DS</sub>=8V were found to be the optimum bias where the device are operating in class-A/AB.

In the second step, the chosen transistor is investigated for its suitability for the SSTWPA application. That is to say, input and output parasitic capacitances, input resistance, output resistance and gain variations as a function of frequency are studied. It is observed that for a given 50 $\Omega$  characteristic impedance, the bandwidth performance of the chosen transistor is limited to 2GHz due to its relatively high 3pF input capacitance. To increase the bandwidth performance, the capacitive coupling technique is employed by sacrificing the overall gain level. In this way the equivalent input capacitance of the transistor reduced to around 1pF where C<sub>c</sub>=2.1pF is taken as an optimized value. Furthermore, the input line is designed for Z<sub>o</sub>~40 $\Omega$  where it is sufficient for a good match to 50 $\Omega$ .

Although these modifications resulted by sacrificing the amplifier gain performance, it enabled the realization of a much wider bandwidth within the operation band of 1-to-8GHz.

Fig. 4. Modified SSTWPA to improve power performance.

Fig. 5. Chip photograph of the fabricated SSTWPA.

The output capacitance of the transistor is approximately equal to 0.5pF. For a maximum voltage swing, optimum-load impedance is obtained to be approximately  $34\Omega$  according to the load-pull simulations. As a result, by using the Eq. 5, optimum inductance  $L_o$  could be determined as 0.57nH. Input line is constructed with using two T-sections, one of which is lossy. Finally, for the biasing purposes at the drain, an on chip inductive transmission-line is constructed to form a wideband RF choke. The fabricated chip photograph of the SSTWPA is shown in Fig. 5 where the die chip dimensions are  $1.31 \times 2.93 \text{ mm}^2$ .

## 4. Results

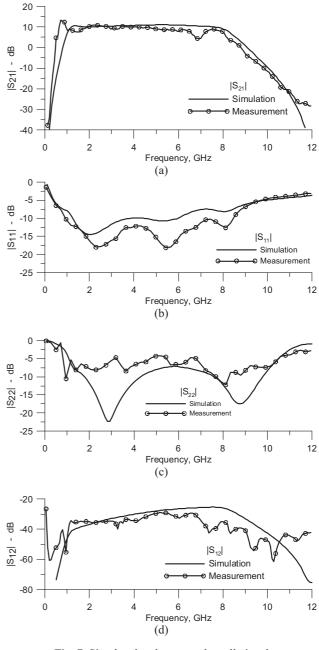

The small signal s-parameter performance of the SSTWPA is shown in Fig. 7 including both simulations and measurements. The chip is bond-wired to an external PCB board for DC supplying purpose. RF signals are left inside the chip and G-S-G type probes and probe station are used for the input and output signal measurements.

The amplifier exhibits an average gain of 10dB across the bandwidth from 1-to-8GHz. The gain can be increased by removing the capacitive coupling, but in doing this would compromise the amplifier bandwidth as mentioned before. Input match ( $S_{11}$ ) of the SSTWPA is below -10dB and the output matching ( $S_{22}$ ) is measured to be -5dB and below for the worst case.

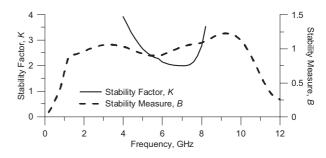

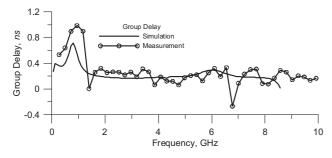

The low frequency mismatch between the simulation and the measurement of the  $S_{22}$  is due to degraded performance of the on chip drain biasing inductance. It is however possible to improve  $S_{22}$  performance by using a suitable external off chip inductance. Fig. 8 shows the group delay performance where the results match quite well with the simulations. For the stability concern, Fig. 6 gives the stability factor (K) and stability measure (B) parameters for simulational stability are that the stability factor is greater than unity and the stability measure is positive. As can be seen from the figure that both K>1 and B>0 are derived inside the band. Also there is not any oscillation condition observed at the output when stimulating input signal when measuring the chip. Therefore, SSTWPA presented a stable operation within the operation band.

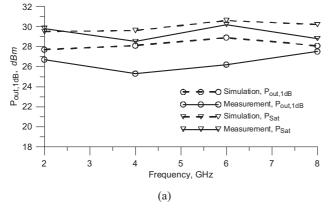

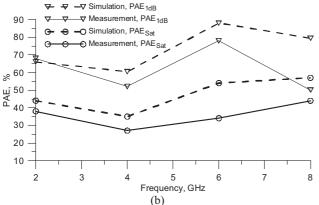

Saturated output power ( $P_{Sat}$ ) and output referred 1dB compression point power ( $P_{out,1dB}$ ) levels are measured and the related power added efficiency (PAE) performances are also calculated using the power measurements in the band of 2-to-8GHz. Results are plotted in Fig. 9.  $P_{Sat}$  and  $P_{out,1dB}$  power levels have their peak values at 1W (30dBm) and 0.5W (27dBm) and PAE levels are above 50% and 27% respectively inside the band.

Fig. 6. Stability performance of the SSTWPA (K>1 and B>0).

Fig. 7. Simulated and measured small-signal s-parameters of the SSTWPA.

(a) Gain, |S<sub>21</sub>| (b)|S<sub>11</sub>| (c)|S<sub>22</sub>| (d) |S<sub>12</sub>|

Fig. 8. Group delay performance of the SSTWPA.

#### 6. Conclusions

This paper demonstrated a special case of a wideband travelling wave power amplifier which uses a single transistor operating in Class-A/AB. Realized single stage travelling wave power amplifier comprised of capacitive coupling and frequency dependent lossy artificial transmission-line to enhance the amplifier frequency-bandwidth product, input match and gain flatness response. Output termination impedance of the amplifier is cancelled and the output-line is comprised of an inductive element to achieve an optimum power-bandwidth performance. The SSTWPA was designed using a 0.25µm GaAs PHEMT process. The fabricated amplifier is shown to provide 10dB gain in the 1-to-8GHz band.  $P_{Sat}$  and  $P_{out,1dB}$  power levels have their peak values at 1W (30dBm) and 0.5W (27dBm) and PAE levels are above 50% and 27% respectively.

## Acknowledgment

The authors wish to acknowledge the assistance and support of The Scientific and Technological Research Council of Turkey (TUBITAK Project-1001-107E253).

# 7. References

- T.T.Y. Wong, "Fundamentals of Distributed Amplifiers" Artech House, Boston, 1993.

- [2] Y. Ayaslı, S.W. Miller, R. Mozzi, L.K. Hanes, "Capacitively Coupled Traveling-Wave Power Amplifier" IEEE Transactions on Microwave Theory and Techniques, Vol. MTT-32, No. 12, pp. 1704-1709, December 1984.

- [3] A.S. Virdee, B.S. Virdee, "Experimental Performance of Ultra Broadband Amplifier Design Concept Employing Cascaded Reactively Terminated Single-Stage Distributed Amplifier Configuration" Electronics Letters, Vol. 36, No. 18, pp. 1554-1555, August 2000.

- [4] B.Y. Banyamin, M. Berwick, "Analysis of the Performance of Four-Cascaded Single-Stage Distributed Amplifiers", IEEE Transcations on Microwave Theory and Techniques, Vol. 48, No. 12, pp. 2657-2663, December 2000.

- [5] B.S. Virdee, M. Yazgi, A.S. Virdee, "Cascaded Single-Stage Amplifier With Improved Gain-Frequency Performance Using Frequency-Dependent Lossy Artificial Lines", Proceedings of the 2nd European Microwave Integrated Circuits Conference (EUMIC'07), pp. 184-186, Munich-Germany, October 2007.

- [6] M. Yazgi, M. Sayginer, A. Toker, B.S. Virdee, H. Kuntman, "Single Stage Travelling Wave Power Amplifier", International Conference on Optimization of Electrical and Electronic Equipment, OPTIM'2010-12th, Romania-Brasow, May 2010.

- [7] K. Krishnamurthy, S.I. Long, M.J.W. Rodwell, "Cascode-Delay-Matched Distributed Amplifiers For Efficient Broadband Microwave Power Amplification", IEEE MTT-S International Microwave Symposium Digest, Vol. 2 of 4, Anaheim, CA, pp. 819-822, June 1999.